"혁신적인 기술력으로 세계 최고를 향해 나가겠습니다."

삼성전자가 3나노 최초 양산에 차세대 반도체 제조기술로 꼽히는 게이트 올 어라운드(GAA) 공정 양산과 선제적인 파운드리 기술로 사업 경쟁력을 강화한다.

삼성전자는 25일 경기 화성 V1라인(극자외선(EUV)전용)에서 차세대 트랜지스터 GAA 기술을 적용한 3나노 파운드리 제품 출하식을 열었다.

GAA 트랜지스터 구조 연구를 2000년대 초 부터 시작한 삼성전자는 2017년 3나노 공정에 적용을 시작으로 지난달 세계 최초로 GAA 기술이 적용된 3나노 공정 양산을 발표한 바 있다.

삼성전자는 3나노 GAA 공정을 고성능 컴퓨터(HPC)에 처음 적용했다. 주요 고객들과 모바일 시스템온칩(SoC) 제품 등 다양한 재품군에 확대 적용을 위해 협력 중이다.

삼성전자는 화성캠퍼스에서 3나노 GAA 파운드리 공정 제품 양산을 시작, 향후 평택캠퍼스까지 확대해 나갈 예정이다.

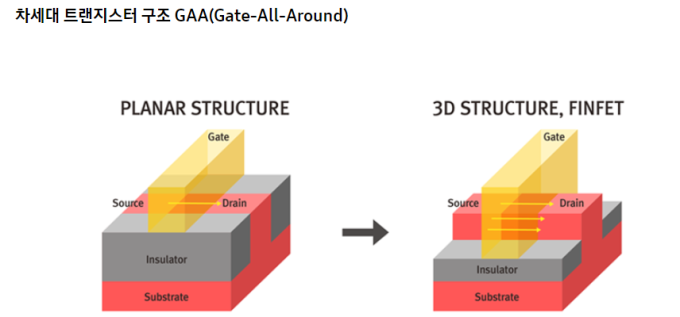

전류의 흐름을 조절해 스위치 역할을 하는 트랜지스터는 반도체의 핵심이다. 트랜지스터에서 중요한 부분이 게이트다. 여기에 전압을 가하면 전류가 흐르고 반대의 경우는 전류가 차단된다. 초고직접회로 시대를 맞아 트랜지스터의 크기도 작아져 이를 정밀하게 제어해야할 필요성이 생겼다.

트랜지스터는 게이트에 전압이 가해지면 채널(Channel)을 통해 소스(Source)와 드레인(Drain)으로 전류가 흐르면서 동작하게 된다.

기존에 사용하던 평판(Planar) 트랜지스터는 게이트와 채널이 하나의 면으로 맞닿아 있는 평면(2D)구조로 트랜지스터의 크기를 줄이다 보면 소스와 드레인 간 거리가 가까워져 게이트가 제 역할을 못하고 누설전류가 생기는 단채널(Short Channel) 현상이 발생하는 등 동작 전압을 낮추는 데 한계가 있었다.

이를 개선하기 위해 입체(3D) 구조의 공정기술이 개발됐다. 이를 핀펫(FinFET)이라고 한다. 구조가 물고기 지느러미(Fin) 모양을 닮았다고 해서 핀 트랜지스터라고 부른다. 게이트와 채널 간 접하는 면이 넓을수록 효율이 높아진다는 점에서 착안해 게이트와 채널이 3면에서 맞닿는 3차원 구조로 접점 면적을 키워 반도체 성능을 향상시켰다.

핀 트랜지스터는 첨단 반도체 공정에 사용되고 있지만 최근 4나노 이후의 공정에서는 더 이상 동작 전압을 줄일 수 없다는 한계가 드러났다. 이를 위해 새롭게 탄생한 것이 차세대 3나노 GAA 구조다.

3나노 이하 초미세 회로에 도입될 GAA구조의 트랜지스터는 전류가 흐르는 채널 4면을 게이트가 둘러싸고 있어 전류의 흐름을 보다 세밀하게 제어하는 등 채널 조정 능력을 극대화했다. 이로 인해 높은 전력 효율을 얻을 수 있다. 이에 삼성전자를 비롯해 TSMC, 인텔 등 반도체 파운드리 업체들이 초미세공정 기술 개발에 열을 올리는 이유다.

경계현 삼성전자 DS부문장 대표이사는 "이번 제품 양산으로 파운드리 사업에 한 획을 그었다"며 "핀펫 트랜지스터가 기술적 한계에 다다랐을 때 새로운 대안이 될 게이트 올 어라운드(GAA) 기술의 조기 개발에 성공한 것은 무에서 유를 창조하는 혁신적인 결과"라고 했다.

이날 출하식에 참석한 이창양 산업통상자원부 장관은 "치열한 미세공정 경쟁에서 앞서기 위해 삼성전자과 시스템반도체 업계, 소부장(소재, 부품, 장비) 업계가 힘을 모아달라"며 "정부도 지난주 발표한 반도체 초강대국 달성전략을 바탕으로 민간 투자 지원, 인력 양성, 기술 개발, 소부장 생태계 구축에 전폭적인 노력을 아끼지 않을 것"이라고 강조했다.

윤은식 기자 eunsik80@kukinews.com